# Breakthrough Packaging Technology Achieves Fully Enabled High Speed & High Density Packaging of Power GaN & SiC

# A Technical Synopsis of IP Purchase Opportunity Courtney R. Furnival

The proprietary Semiconductor Packaging Solutions µMaxPak technology offers quantum improvements for high speed, high voltage and high power devices in near chip-scale surface mount (SMD) packages. These performance improvements are enabled by extremely low inductance, electrical resistance, and thermal resistance. The proprietary architecture is leadless and wire-bondless, and accommodates vertical integration of cascode switches, gate drivers, magnetic isolators and other functions/components. The µMaxPak is ideal for high power 600V & 1200V switches, and these advantages become essential for wide band-gap (WBG) power devices at larger currents and higher speeds. The μMaxPak architecture is protected by U. S. patent 9,214,416 issued 12/15/15, and key to evolving GaN & SiC power device operation at optimum performance & efficiency, and even improves performance & efficiency of high speed Si power devices. The µMaxPak implementation can be Laminate-based LGA or Leadframebased QFN/DFN with lateral or vertical power die, and is compatible with existing commercial assembly technology and equipment. The numerous technology benefits are broad & scalable, enabling higher efficiency & power density for diverse applications. The near chip-scale µMaxPak architecture virtually eliminates WBG package performance constraints, and is enables direct die-to-Cu interface of smaller WBG power die. Furthermore, SMD devices that are under-filled, coated or potted are absolutely the best way to manage high voltage (HV) spacing/creepage and system integration, which are required for increased power-densities.

#### µMaxPak Enables Half-Bridge with 5x5mm Die

Ultra-Fast GaN & SiC Switching >100 MHz

Negligible + to - Inductance <0.1 to 0.2nH

Ultra Low + to - Resistance <100 to 200µohm

Low Thermal Resistance, Die-Case 0.1°C/W

Switching Voltage Scalable to >2,000Vp

High Temperature Operation, Tj(max) >185°C

Maximum Efficiency for GaN & SiC to >99%

Accommodates HV IEC, EN & UL Pollution 1 External Pad Spacing with under-fill, coating or potting

Displaces many Hi-Power Hi-Voltage DBC Modules

Multi-chip Die Switches are Ideal, SS, HB FB, etc.

Vertical/3D Topology with integrated cascode, gatedrivers & other components

Optimum Wide-Band die yield with pre-tested building blocks for Power PCBs or DBC Modules

Reduced Package NRE, Risk & Development Time Low Cost QFN Leadfame or Laminate Platform

#### **HV Power GaN Applications:**

<u>Present:</u> 200-650V @ 10-50A for PFC, Solar Inverters & Power Supplies (TO220/247 & Limited leadless SMD)

Near-Term: EV/HEV, UPS & Industrial Motor Drives are increase to 100s of Amps

Future Potential: Add 1200V & increase current further

## **HV Power SiC Applications:**

<u>Present:</u> 1200V & Up @ 50-100A Solar Inverters, P.S. & UPS. (TO220/247 & diodes in DBC modules)

Near-Term: Industrial Motor Drives & Traction with Full (FET/Diode) SiC DBC modules at increasing speed, and at current to hundreds of amps & thousands of volts

<u>Future Potential:</u> EV/HEV, Wind Turbine & Electric Grid with ever increasing currents & voltage

# **HV Power Si Applications:**

Advanced and Evolving Fast IGBTs & Power HV FETs in all existing applications

March 2017 1

### Package Innovation & µMaxPak Patent

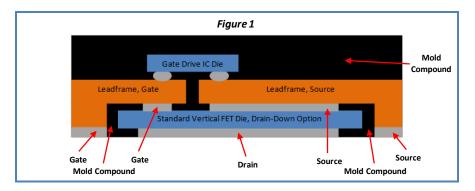

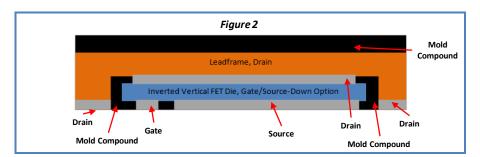

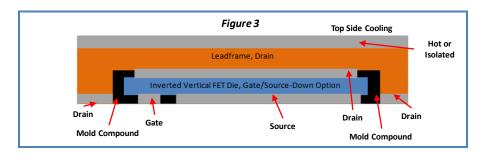

The  $\mu$ MaxPak packages are near-chip-scale SMD molded packages, and typically Dual- or Quad-Flat-No Lead (DFN or QFN) packages with open power die cavity(s) in bottom of package. The bottom cavity(s) offer direct mechanical, thermal & electrical connection between exposed power die and user mother-board or substrate, and the leadframe or laminate copper makes thermal and electrical connections between the top-side of power die and additional package bottom pads. The cavity allows double-side leadframe or laminate assembly with top-side available for vertical integration with bump-chip or SMD components like cascode switches, gate drivers, isolators and other components, or in some configurations direct top-side heatsink or cold-plate. The Figures 1, 2 & 3 architectures show leadframe-based  $\mu$ MaxPaks, but are equally applicable to laminate-based  $\mu$ MaxPaks.

Figure 1: μMaxPak Single-Switch (SS) Cross-section showing vertical power FET die in bottom-side leadframe cavity with gate & source connected to leadframe, and gate drive IC output connected to top of FET gate pad.

Figure 2: μMaxPak Single-Switch Cross-section showing inverted vertical power FET die in bottom-side leadframe cavity with drain connected to leadframe.

Figure 3: Rugged leadframe structure showing inverted vertical power FET die in bottom-side leadframe cavity with drain connected to leadframe, which can be clamped between top & bottom cold plates for high power dissipation in applications like EV/HEV.

Power die can be a) lateral or vertical, b) normally-on or normally-off, and c) Si, SiC or GaN, and all connections can be bump-pad (No WBs). This structure provides geometrically ideal high-current interconnects with virtually zero length, and maximum copper width and thickness. This accommodates gate driver outputs sitting directly above switch gate & sense pads. The tight near chip-scale die packaging is ideal for paralleled die, and offers significantly better performance if HB, FB & 3-Phase switches are co-packaged.

March 2017 2

Laminate-based  $\mu$ MaxPak best accommodates complex interconnects at low to medium power, and Leadframe-based  $\mu$ MaxPaks are most rugged providing lowest R, L and Rjc for higher power & higher switching speeds.

The well controlled and proven DFN/QFN processes/materials can accommodate HV external pad separation for UL pollution 1 minimum spacing for voltage to 1200Vp and higher, allowing high package power-densities to be extended to the mother-boards, modules or full systems.

The μMaxPak IP is protected by U.S. Patent, "High Speed, Low Loss and High Density Power Semiconductor Packages (μMaxPak) with Molded Surface Mount High Speed Devices(s) and Multichip Architectures(s)". The patent shows numerous examples of μMaxPak configurations including:

- Standard & Inverted Die

- Vertical & Lateral Die

- Diode, IGBT, FET, JFET & BJT Die

- Leadframe & Laminate (LGA) based packages

- Single-Switch & Half-Bridge (Half-Bridge is preferred/optimum)

- Vertical Integration of Cascode FET, Gate-Driver IC & passive components

- Thin Type architecture with leadframe exposed on both top & bottom for extreme ruggedness and maximum power dissipation.

- The unique and proprietary μMaxPak architecture can be assembled on commercial standard assembly lines, thereby reducing cost, risk and development/startup time.

The  $\mu$ MaxPak architecture's near zero packages Rjc must be used on thermal mother-boards to fully utilize their potential. Laminate power PCBs with heavy Cu, thermal via, thermal pre-preg, embedded heat-slugs are practical and economical, and at the highest power levels DBC mother-boards are required. The Power PCB and DBC can be enhanced with heatsinks and convection at higher power levels, and in some cases the

μMaxPak can be used as pre-tested building blocks for conventional high power DBC modules.

#### Competitive Advantages

| WBG Package Type       | D <sup>2</sup> Pak&TO220-247 | LGA QFN             | Power PQFN       | μMaxPak             | μMaxPak            |

|------------------------|------------------------------|---------------------|------------------|---------------------|--------------------|

| Package Architecture   | Custom Multi-Chip            | Lamiante-Based      | LF w Solder Clip | Laminate-Base       | Leadframe-Base     |

| Parasitcs(L)           | High                         | Moderate            | Low              | Very Low            | Near-Zero          |

| Package Losses(R)      | High                         | Moderate            | Low              | Low                 | Lowest             |

| Thermals(Rjc)          | Low                          | Moderate            | Low              | Low                 | Lowest             |

| Power Density          | Low                          | Moderate            | High             | High                | Highest            |

| SMD                    | D2Pak only                   | YES                 | YES              | YES                 | YES                |

| Leadless               | NO                           | YES                 | YES              | YES                 | YES                |

| Wire Bondless          | NO                           | YES & NO            | YES              | YES                 | YES                |

| Max BV                 | 600/1200(TO247)              | 600/1200            | 600/1200         | 600/1200            | 600/1200           |

| Max.Current, 600V(2)   | <50A(D2Pak/T0220)            | <50A                | 50A              | 150A                | 200A               |

| Max.Current, 1200V(1)  | 50A(T0247)                   | <50A                | <50A             | 75A                 | 100A               |

| Switches, Potential    | SS                           | SS/HB/FB/3P         | SS/HB            | SS/HB/FB/3P         | SS/HB/FB/3P        |

| Integration, Potential | Cascode                      | Cascode/GD/isol/etc | Cascode          | Cascode/GD/isol/etc | Cascode/GD/isol/et |

| Complexity             | High                         | Moderate            | Moderate         | Low                 | Lowest             |

| Manufacturability      | Fair                         | Good                | Poor             | Good                | Good               |

| Value                  | Poor                         | Fair                | Poor             | Good                | Best               |

| Cost                   | Marginal                     | Low                 | High             | Low                 | Low                |

NOTES:

- 1. µMaxPak is a proprietary DFN/QFN architecture offered with package constraints shown.

- 2. Typical maximum continuous GaN & SiC currents of available HV SiC & GaN products.

- 3. μMaxPak highlighted parameters are as good as or better than the best competing packages.

- 4. To accommodate GaN and SiC, the TO-220, D2Pak, TO247, and PQFN assemblies are non-std & complex with multi-components, isolators, etc.

### **Power Density**

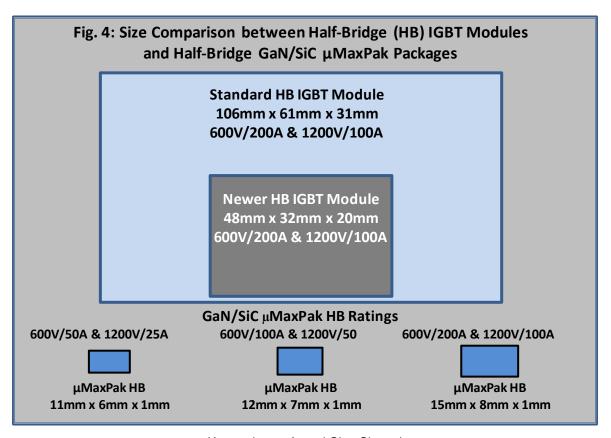

The  $\mu$ MaxPak power-density is enabled by improvements in die power-density & efficiency. If we assume GaN & SiC die power-density are increased by a factor of 10 and losses reduced by a factor of 5, the potential  $\mu$ MaxPak sizes with 5x5mm power die are shown in Figure 4 with standard 600/1200V IGBT modules. These assumptions are conservative, relative to the potential of wide band-gap power devices. Today most Power GaN & SiC devices are being sold for lower currents & operating frequencies, and usually in leaded TO220 & TO247 packages, despite the introduction of a number of leadless laminate & leadframe based SMDs. Still, the  $\mu$ MaxPak enables the best available improvements in both Power-Density & Performance.

(Approximate Actual Size Shown)

Courtney Furnival of Semiconductor Packaging Solutions has over 30 years in high volume semiconductor packaging experience. He also has 10 years experience designing custom DFN & QFN packages for high-power, high-voltage and high frequency applications that include power MOSFET, Power ICs, and IGBT modules for major companies, and has designed numerous power GaN & SiC packages for key companies in recent years. The proprietary µMaxPak architecture is a direct extension of this experience. He has successfully managed a number of high volume production facilities during those years. With that experience, he has very effective guided Asian packaging houses from prototype designs through pilot runs to full production for various top industry semiconductor companies. This guidance included maximizing throughput, quality, and reliability, while minimizing cost. Courtney Furnival holds a bachelor degree in Physics, with minors in Chemistry, and Mathematics. He has completed his course work towards a PhD in Physics. He started his work in a Power and RF electronic packaging material and process R &D center. Courtney Furnival holds numerous patents on power modules and semiconductor packages, and special processes and manufacturing techniques of electronic high volume packages.

Presented by **Anagenesis, Inc.**222 North Sepulveda, Suite 2000, El Segundo, California, 90245

Contact: Arnold Alderman

arnold.alderman@anagenesis-inc.com

Office: 310 662 4764 Cell: 310 704 7079

March 2017 4